# Towards Predictable Execution of Safety-Critical Tasks on Mixed-Criticality Multi-Core Platforms

Pls:

Harini Ramaprasad Dimitri Kagaris **Students:** Anthony Kulis Aishwarya Vasu Ashish Choudhari

Southern Illinois University Carbondale

# **Project Overview and Description**

## Motivation

• Multi-core architectures→high performance, low power

## Problem

Deterministic execution of highly safety-sensitive (HSS) tasks in presence of less safety-sensitive (LSS) ones is challenging due to shared resources

## Viable Solution

Virtualization (hypervisor) for isolation of HSS & LSS task sets

## Project Description

Comprehensive trade-off study of *determinism* vs *performance* of mixed-criticality tasks executing in the Freescale P4080 multi-core platform

# Approach

- Explore time and space partitioning of resources among task sets executing within real-time and general-purpose operating systems

- Develop heuristics for time-efficient solutions

- Employ a two-stage approach

- **Stage 1:** aggregate requirements of tasks within each OS and study determinism and responsiveness across OSs

- **Stage 2:** study determinism and responsiveness of individual tasks within each OS

- Metrics for measuring success of resource allocation

- HSS tasks: determinism of execution (satisfaction of timing and precedence constraints

- LSS tasks: Quality-of-Service (QoS)

- Experimental platform → *Freescale QorlQ P4080*

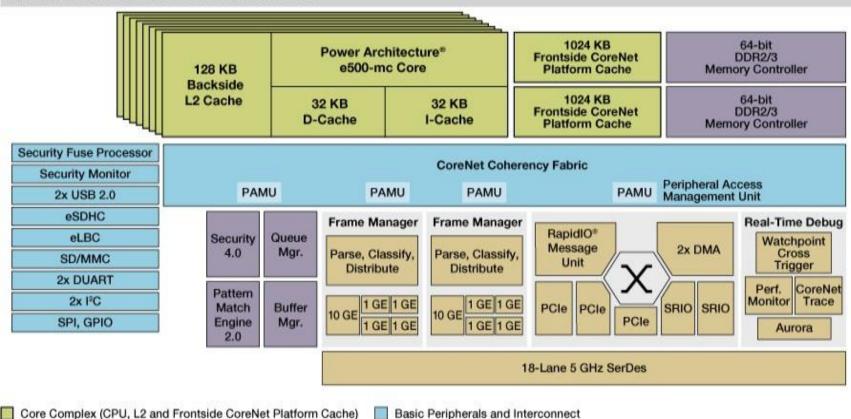

# **P4080 Development System**

P4080

Picture from: 2004-2013 Freescale Semiconductor, Inc.

**QorlQ P4080 Communication Processor**

Accelerators and Memory Control

Networking Elements

# **Technical Detail**

#### Freescale QorlQ P4080

- 8 high-performance cores with private L1, L2 and shared L3.

- Embedded hypervisor

- Safe OS partitioning and support for partitioning cores, memory and I/O devices.

- High-bandwidth communication & coherence infrastructure

- Support for prioritization, bandwidth allocation, packet-level queue management and QoS scheduling

- Suitability of Freescale P4080 platform

- Scheduling granularity is coarse which allows static partitioning of resources. Suitable for systems with HSS tasks where determinism is paramount

- Hypervisor design exploits hardware mechanisms in cores to improve efficiency of virtualization. Easier to bound hypervisor interference across OSs

- Benchmarks for creation of mixed-criticality task sets

- MRTC WCET benchmarks

- EEMBC benchmarks: LMBench, CoreMark, perf\_measure(RCI)

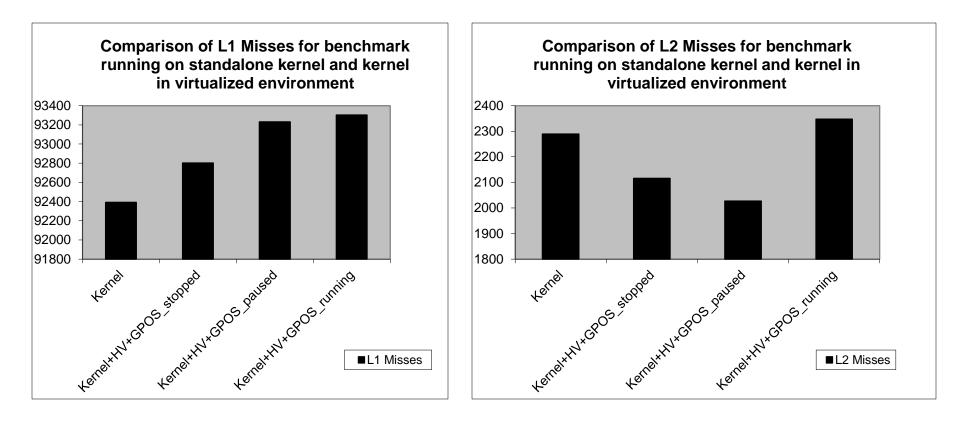

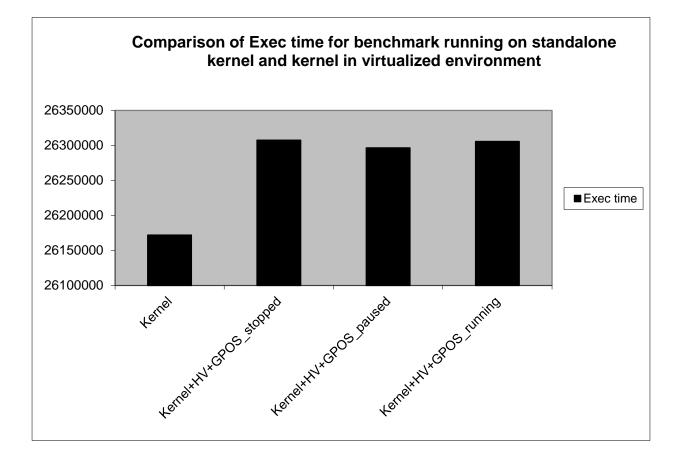

#### RT Performance comparison between Virtualized and non-Virtualized mode

- Study overheads due to the presence of hypervisor

- Execute on standalone kernel and virtualized kernel

- Study L1, L2 behavior and task execution times

- Study performance of tasks on RT partition

- Execute HSS tasks in RT partition

- Vary memory usage in GP partition and study effects on tasks in RT partition

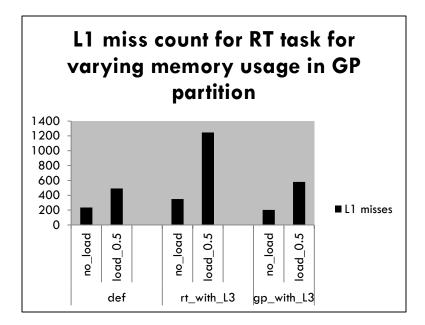

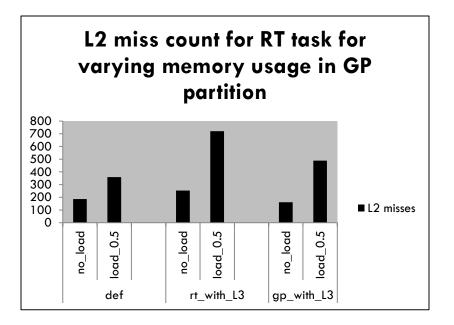

## L1 and L2 cache misses

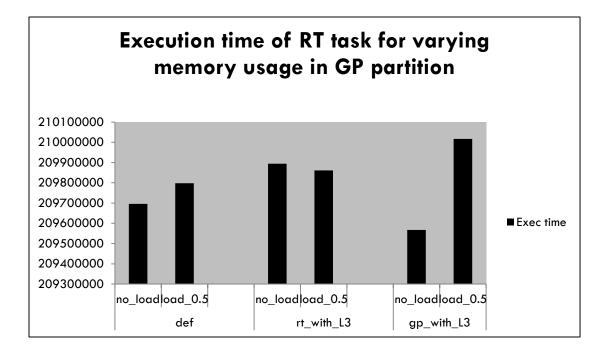

### **Execution time**

# L1 and L2 cache misses for varying memory usage in GP partition

# Execution time of RT task for varying memory usage in GP partition

## **Observations**

- Problems

- Hypervisor allows multiple partitions, but adds overhead

- Execution time of tasks on RT partition (HSS tasks)

- Increases when there is memory load on GP partition

- Is sometimes inconsistent across multiple runs

- Potential solutions

- Lock cache lines tasks on RT partition to improve predictability

- Partition cache among guest RT & GP OSs to improve determinism and responsiveness of tasks on RT partition

# References

- S. Xi, J. Wilson, C. Lu and C. Gill. "RT-XEN: Towards Real-Time Hypervisor Scheduling in Xen." In Proceedings of the 9thACM international conference on Embedded Software (EMSOFT), 2011.

- R. Fuchsen. "How to address certification for multi-core based IMA platforms: Current status and potential solutions." In Proceedings of the Digital Avionics Systems Conference (DASC), 2010.

- C. Ault. "Challenges of safety-critical multi-core systems." White paper, Wind River Research.

- P. Baltham, et al. "Xen and the art of Virtualization," In Proceedings of SOSP '03 19th ACM Symposium on Operating systems principles.

- Jun Zhang; Kai Chen; Baojing Zuo; Ruhui Ma; Yaozu Dong; Haibing Guan. "Performance analysis towards a KVM-Based embedded real-time virtualization architecture." 5th International Conference onComputer Sciences and Convergence Information Technology (ICCIT), 2010, pp. 421 – 426.

- M. Peshave. "High-Assurance Reconfigurable Multicore Processor Based Systems." In Proceedings of the 13thIEEE International Symposium on High-Assurance Systems Engineering (HASE), 2011.

- M.S. Mollison, J.P. Erickson, J.H. Anderson, S.K. Baruah and J.A. Scoredos. "Mixed-Criticality Real-Time Scheduling for Multicore Systems." In Proceedings of the 10<sup>th</sup>IEEE International Conference on Computer and Information Technology (CIT), 2010.

- Freescale Inc. "P4080: QorIQ P4080 Eight-Core Communications Processors with Data Path." <u>www.freescale.com/webapp/sps/site/prod\_summary.jsp?code=P4080</u>devicesolutions.net "Topaz\_i.MX25 CPU Module Technical Reference Manual." <u>http://devicesolutions.net/LinkClick.aspx?fileticket=hS62BQTuyhM%3D&tabid=305</u>

- Adventium Labs. "MiCART Mixed-Criticality, Real-Time Virtualization Support." www.adventiumlabs.com/?q=productsandservices/micart

- "Lmbench Tools for Performance Analysis." <u>http://www.bitmover.com/lmbench/</u>

- "MRTC WCET Benchmarks." <u>www.mrtc.mdh.se/projects/wcet/benchmarks.html</u>